In this post we are going to share with you the Full Adder Verilog Code using two Half Adders. The verilog code of full adder using two half adder and one or gate is shown below.

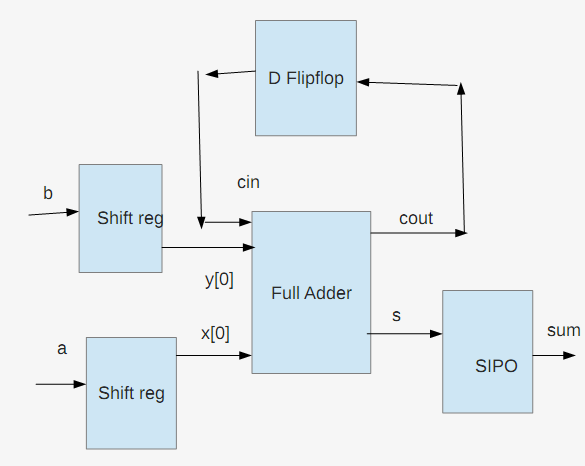

This repository contains behavioral code for Serial Adder.The following individual components have been modeled and have been providedwith their corresponding test benches:

- Parrallel Input Serial Output Shift register (PISO) (

piso.v) - D Flip Flop (

d_flipflop.v) - Full Adder (

full_adder.v)

File

serial_adder.v is the master node, the corresponding testbench isserial_adder_tb.v. To compile and visualise the waveforms (using iverilogand gtkwave), follow these steps:- Install

iverilogandgtkwaveusing the instructions given here. - Clone this repository using the command

git clone https://github.com/RJ722/serial-adder-verilog. cd serial-adder-verilogiverilog -o serial_adder.out serial_adder_tb.v./serial_adder.outgtkwave serial_adder_tb.vcd # Visualise waveforms

For changing the input values to the adder, please make changes in

serial_adder_tb.v.